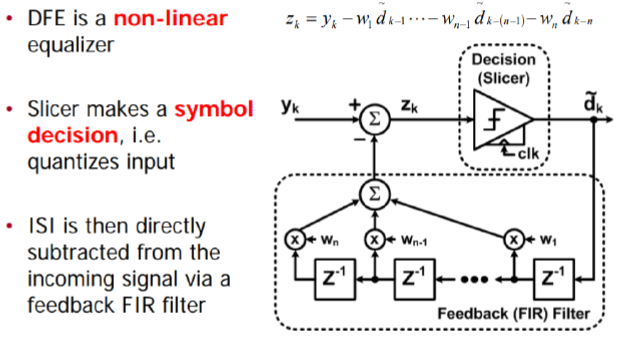

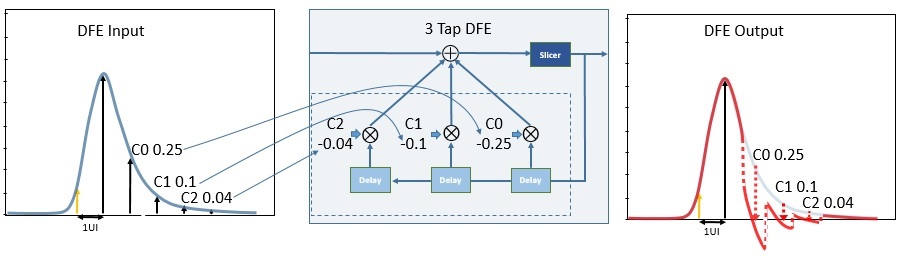

IBIS/AMI: Equalization in coming DDR standard | SPISim: EDA for Signal Integrity, Power Integrity and Circuit Simulation

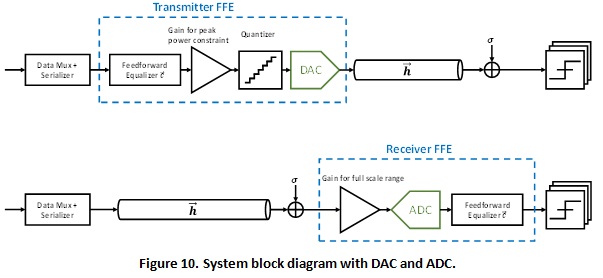

Feedforward Equalizer Location Study for High-Speed Serial Systems | 2019-04-29 | Signal Integrity Journal

Figure 1 from A 70 mW 25 Gb/s Quarter-Rate SerDes Transmitter and Receiver Chipset With 40 dB of Equalization in 65 nm CMOS Technology | Semantic Scholar

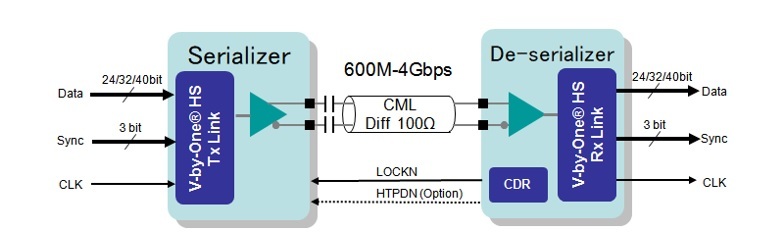

The technology of V-by-One® SerDes apply not only to TV application but to high-speed interfaces for communication/computer/industrial equipment as well|THine Electronics

Feedforward Equalizer Location Study for High-Speed Serial Systems | 2019-04-29 | Signal Integrity Journal

PDF) System Level Optimization for High-Speed SerDes: Background and the Road Towards Machine Learning Assisted Design Frameworks

a) Conventional high-speed links with independent data recovery loop... | Download Scientific Diagram

The technology of V-by-One® SerDes apply not only to TV application but to high-speed interfaces for communication/computer/industrial equipment as well|THine Electronics